CAN 소개

비트 스터핑

완료 조건

오류 플래그

정상적인 데이터 전송을 위한 기본적인 전제 조건은 동기화된 통신 파트너가 있어야 한다는 점입니다. 시작 비트의 우성-열성 신호 에지(dominant-recessive signal edge)는 CAN 메시지의 동기성을 만듭니다(프레임 시작-SOF). 그 후 메시지 전송 과정 끝까지 동기성을 유지하기 위해 재동기화 메커니즘이 사용됩니다.

재동기화

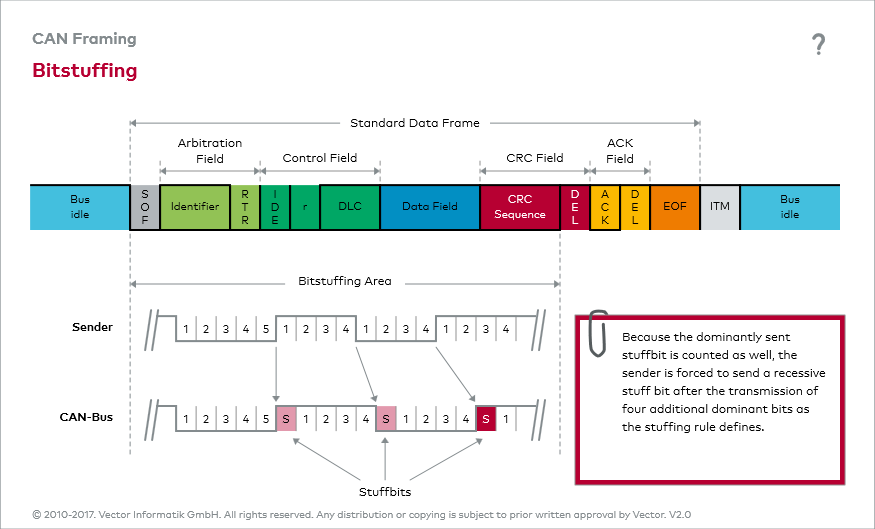

재동기화 메커니즘은 열성-우성 신호 에지에 대한 평가에 기초합니다. 비트 스터핑 메커니즘 (bit stuffing mechanism)이라고 불리는 과정이 이러한 신호 에지를 보장합니다. ISO 11898-1은 트랜시버가 다섯 개의 동일한 비트를 전송할 때까지 보조 비트를 전송해야 한다고 규정합니다. 다섯 개의 동일한 비트에 이어 보조 비트가 나타날 때에도 스터프 비트(stuff bit)가 추가됩니다.

비트 스터핑 구역

비트 스터핑이 SOF를 전송함으로써 시작되고 CRC 시퀀스의 마지막 비트를 전송하여 끝나기 때문에, 데이터 필드가 8바이트로 이루어진 표준 포맷의 데이터 프레임에서 발생할 수 있는 최악의 경우의 스터프 비트의 이론적 숫자는 24개입니다. 따라서 표준 포맷에서 이론적으로 가능한 데이터 프레임의 최대 길이는 132비트입니다.

다음의 그림 “비트 스터핑”을 통해 비트 스터핑 메커니즘을 학습할 수 있습니다.

마지막 수정됨: 목요일, 22 8월 2019, 8:26 AM